★北京广利核系统工程有限公司程康,李明钢

关键词:FPGA;点对点通信;安全级DCS

反应堆保护系统(RPS)作为核电安全级离散式控制系统(DCS)的组成部分,是公认的核电站最重要的安全保障系统,其作用为运行参数达到核安全保护屏障阈值时,紧急停闭反应堆,可以避免核安全事故发生。由于对停堆响应的处理涉及到核电站人员、设备和环境的安全,因此,安全级DCS系统指标对停堆响应时间有着非常严格的要求。无论是美国核管会标准评审大纲(NUREG-0800)还是环保部的相关标准(HAD102/16)都对停堆响应时间做出了指导性的说明,停堆响应时间通常应小于0.2s[1][2]。因此,如何减小停堆响应时间,是安全级DCS系统设计中必须要考虑的一个重要因素。

在安全级DCS系统中,停堆响应时间是指从传感器采集到信号到反应堆保护系统输出信号再到停堆用电路器所需要的时间,其经过模拟量输入(AI)、I/O总线处理、点对点网络通信、主处理器中央处理器(CPU)运算、数字量输出(DO)等过程。目前,绝大多数研究机构和DCS生产厂商通过优化AI、DO模块选型、I/O总线端口、CPU应用程序算法等方式减少停堆响应时间[3],但是鲜有通过提高网络通信的效率来优化停堆响应时间的研究。本研究提出了一种利用可靠性高、速度快、并行处理等优势的FPGA技术来改进当前通信系统,极大地提高了多通道、大数据容量的点对点通信处理效率,从而对停堆响应时间进行了优化。本文首先介绍了数字化反应堆保护系统的架构及停堆响应时间的计算方法;其次,进一步分析了影响停堆响应时间的因素并且提出了通过点对点通信优化停堆响应时间的可能性;最后,利用FPGA技术优化实现点对点通信并且进行了实验验证,证明了此方法对优化保护系统停堆响应时间有着积极贡献。

1 反应堆保护系统的停堆响应时间

1.1 数字化反应堆保护系统架构

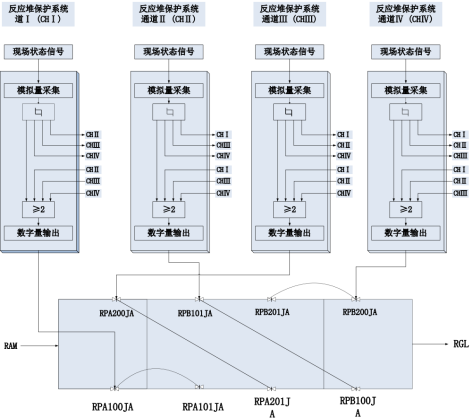

一个典型的数字化反应堆保护系统如图1所示,从最高级别的安全性考虑,反应堆保护系统采用4通道(CH I、CH II、CH III、CH IV)冗余设计,每个通道相对于其他通道独立工作且均对应一组测量过程参数传感器(如温度、流量、液位、压力等),在每个通道上进行阈值比较,得出一个“是否超限”的结果,并将此结果发送到其他的通道。每个通道对本通道的阈值比较结果和其他三个通道的阈值比较结果进行“四取二”的逻辑表决,并将结果输出至该通道断路器的失电停堆线圈[4]。

图1 反应堆保护系统示意图

1.2 反应堆保护系统信号处理过程

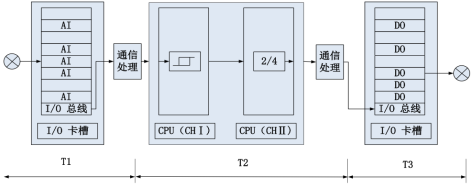

反应堆保护系统信号处理过程如图2所示,在DCS系统中,AI模块通过传感器采集现场的工况信号,经过总线管理模块后,信号被送至CPU模块,CPU模块进行运算处理后将输出结果通过点对点通信模块,并且在接收到其他通道通过点对点通信传来的信息后进行再次处理。最后,通过总线管理模块将CPU处理后的结果发给DO模块,最后由DO实现输出[4]。

图2 反应堆保护系统信号处理示意图

1.3 停堆响应时间的计算

图3 反应堆保护系统响应时间的计算

根据上述介绍,停堆响应时间的计算可以分为三部分,如图3所示,系统响应时间TRT为TRT=TRPC(输入1)+T点对点+TRPC(开关量输入)。

1.4 停堆响应时间分析

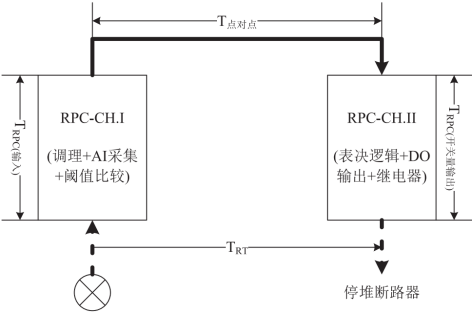

以中国首套拥有自主知识产权的核电安全级DCS和睦系统FirmSys为例,其组成部分与计算,如图4所示[5]。

图4 典型反应堆保护系统响应时间计算

在典型的FirmSys系统应用的实例中,主处理模块周期(tMPU)、I/O通信模块周期(tSCU)、网络通信模块周期(tNCU)和I/O周期(tIO)通常分别设置为15ms、8ms和8ms。因此,按照上述算法,停堆响应时间计算如下:

TRT=TRPCi+1.7TMPU1+2TNCU1+TTrans+1.7TMPU2+2TNCU2+TRPCo

=32+1.7×15+2×8+1.7×15+2×8+32=149(ms)

2 点对点通信对停堆响应时间的影响

2.1 对停堆响应时间影响分析

根据前一章节的描述,我们知道影响停堆响应时间的主要因素为CPU中各模块的处理时间。CPU模块所承担的功能比较复杂,需要从接收AI模块的信号、进行阈值比较、将比较结果通过点对点通信发送到其他通道、接收其他通道通过点对点通信传送的数据,到再次进行阈值比较、产生DO模块输出信号。换句话说,CPU模块的处理可以划分为三个具体的模块:主控制器模块、IO数据与总线处理模块、点对点通信模块。因此,如果对上述的三个具体模块进行优化,便可以减小停堆响应时间以提高保护系统的效率。由于在其他研究中对主控制器和IO数据与总线处理部分的研究已经较为成熟,在本研究中我们仅讨论目前研究较少的点对点通信模块部分的优化。

2.2 点对点通信的处理机制

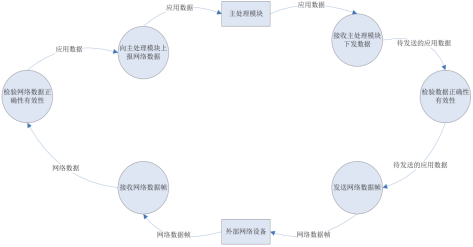

点对点通信模块为控制站的主处理模块提供网络数据的收发,实现框图如图5所示。在发送时,主处理模块将待发送的数据放置在双口RAM中,点对点通信模块读取到双口RAM的信息后进行数据有效性校验,通过校验后的数据通过网卡发出;在接收时,点对点通信模块通过网卡接收到信息后进行数据有效性校验,通过校验后将数据存入到双口RAM中待主处理模块读取。

图5 点对点通信的数据处理流程

同时,为了核电站的安全性考虑,网络通信模块除了与主处理模块通过双口RAM交换数据和与其他站点的网络设备通信模块进行通信外,根据CEI/IEC60880等规范,它还要实现模块自诊断、状态显示接口、热备冗余处理、周期性维护等功能[6]。

2.3 点对点通信对停堆响应时间的影响

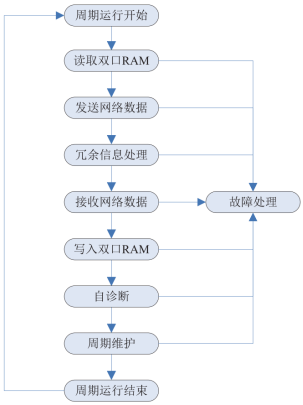

图6 点对点通信模块流程图

基于微处理器的特点,点对点通信模块各项功能是周期运行的,每一个微处理器在执行周期中所执行的任务如图6所示,每一项子任务均按顺序执行,因此网络通信模块的最小执行周期为每项子任务的周期之和。

3 利用FPGA技术优化实现站间点对点通信

在原来微处理器的方案基础上,对点对点通信模块做出最小的改动,使用FPGA+双口RAM的解决方案,可以极大地改善点对点通信的处理周期。

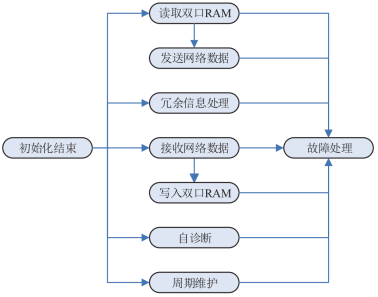

3.1 任务的并行处理

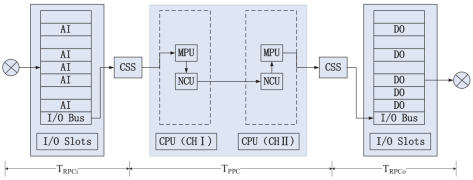

由于FPGA的并行处理能力[7],每一个子任务在FPGA中均可以同时执行。基于FPGA架构的点对点通信模块的处理框图如图7所示。

图7 基于FPGA技术的点对点通信模块流程图

3.2 对网络数据收发的优化

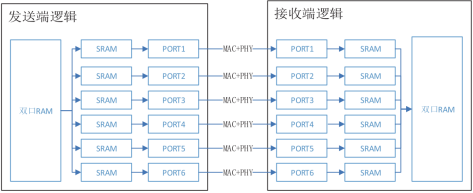

对于微处理器的从网络端口1到端口6轮询的数据收发模式,FPGA的并行处理能力允许系统同时对6个端口的数据进行发送,并且随时对任一端口的网络进行接收并且缓存,极大地提高了网络数据收发的执行速度,缩短了6个端口网络的收发总体时间。

图8 点对点通信网络收发功能框图

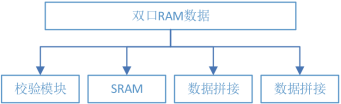

基于FPGA的6端口的点对点网络通信模块的网络数据收发功能框图如图8所示。由于双口RAM不能对同一个地址进行操作,在FPGA中利用状态控制双口RAM的读写顺序,可以避免同时对同一地址的双口RAM进行操作。

在发送网络数据的处理中,通信模块从主处理模块读取到待发送数据之后同步进行位宽转换(32-bit到8-bit)后存入到相应的SRAM中,数据读取完成并且通过校验后,会通过网卡立即将6个端口的网络数据同步发出。

在接收网络数据的处理中,当检测到某个或多个网卡有数据接收后,FPGA逻辑会立即对数据进行处理,并存储到相应的SRAM中,同时进行数据有效性校验,如果不通过则立即报错。在系统执行写双口RAM操作时,将数据进行位宽转换(8-bit到32-bit)后存入到相应的双口RAM中。

因此,在发送数据时,由于FPGA处理可以完成数据有效性校验、将数据存储到SRAM、6个端口同时发送,因此较微处理器的执行方式至少节省了数据存储器间转移复制、位宽转换和5倍同一网卡发送的时间。同理,在接收数据时,FPGA处理的方式节省了5倍SRAM复制、存储期间数据复制和位宽转换的时间。

3.3 对双口RAM处理的优化

图9 从双口RAM读取数据的并行处理FPGA

对主处理模块交互的双口RAM的处理如图9所示,FPGA在读取双口RAM中的数据的同时,还进行数据缓存、数据拼接、数据校验和数据状态解析等处理。

在读取双口RAM数据时,FPGA直接输出信号访问双口RAM的相关引脚,并直接从双口RAM获取数据到FPGA内部寄存器,得到的数据同时读取到SRAM、相关状态寄存器和数据有效性校验模块中,相当于完成了微处理器的三个顺序执行任务的工作量。

3.4 基于FPGA实现点对点通信方案的测试

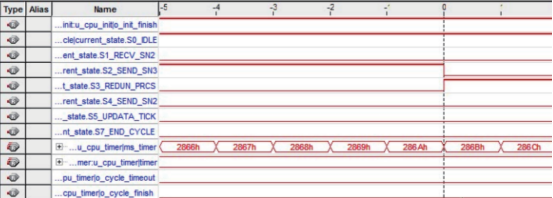

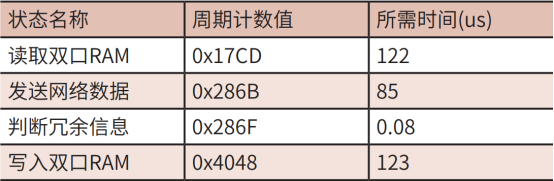

在线逻辑分析仪的使用,如Altera的SignalTap或Xilinx公司的ChipScope对FPGA内部的信号进行抓取,为我们提供了测试基于FPGA的点对点通信模块的手段[8]。在周期计数器中加入测试点,测试每一个状态完成后的周期计数器时间,就可以测出通信模块周期运行时每个状态所需要的时间,如图10所示。在状态机发送网络数据执行完成后,SingnalTap抓取周期计数器的值为0x286A,时钟周期为50M,因此状态机执行读取SN2数据和发送网络数据所用的时间为206.92us。表1中列举了经过换算后的每一个状态所需要的时间。

图10 SingnalTap抓取发送网络数据后周期计数器的值

表1 状态机各状态需时间

将接收网络等待时间设为500us,由表1数据可以计算出网络接收数据所需要的时间大约为122+85+0.08+123+500=830us,粗略记为1ms。将此数据代入计算公式,重新计算系统响应时间约为:

TRT=TRPCi+1.7TMPU1+TPPC+1.7TMPU2+2TNCU2+TRPCo

=32+1.7×15+0.8+1.7×15+32=117.8(ms)

由此可知,采用FPGA技术点对点通信在原系统中可使响应时间缩短31.2ms。

4 结论

本文分析了基于FPGA技术点对点通信对核电安全级DCS停堆保护响应时间的影响,提出了设计和解决方案,进行了理论计算,并利用在线逻辑分析仪对方案进行了测试和验证。结果表明,由于FPGA具有速度快、并行执行等特点,利用FPGA技术实现点对点通信,可以极大优化停堆保护的响应时间。

FPGA技术的应用是未来核电安全级通信发展的方向,目前对于FPGA技术在核电安全级DCS设备上并没有得到广泛的应用。在以后的研发过程中,利用FGPA实现安全级DCS的其他设备和功能是未来核安全级保护系统的研究方向。

作者简介:

程 康(1983-),男,高级工程师,硕士,现就职于北京广利核系统工程有限公司,主要从事核安全级仪控系统设计方面的研究。

李明钢(1977-),男,河南平顶山人,高级工程师,学士,现任北京广利核系统工程有限公司副总经理,主要从事核电仪控系统设计制造生产管理相关工作。

参考文献:

[1] NUREG-0800,Guidance on Digital Computer Real-Time Performance[S].

[2] HAD102/16, 核动力厂基于计算机的安全重要系统软件[S].

[3] 郑伟智, 李相建, 朱毅明. 核电站数字化反应堆保护系统停堆响应时间分析[J]. 自动化博览, 2010, 8 : 74 - 76.

[4] 汪绩宁, 周爱平, 郄永学, 等. 核电厂反应堆保护系统紧急停堆响应时间分析及测试[J]. 核动力工程, 2012, 33 (2) : 5 - 10.

[5] 张冬冬, 蒙海军. 红沿河核电站安全级DCS 控制系统[J]. 电力建设, 2009, 6 : 66 - 68.

[6] CEI/IEC 60880, Nuclear power plants-Instrumentation and control systems important to safety-Software aspects for computer-Based systems performing category a functions[S].

[7] McNelles P, Lu L. A review of the current state of FPGA systems in nuclear instrumentation and control[C]. //AMSE, Proceedings of the 2013 21st International Conference on Nuclear Engineering, Chengdu : ICONE21.

[8] Intel. Intel Quartus Prime Pro Edition User Guide[R]. USA : Intel Corporation. 2018.

摘自《自动化博览》2023年10月刊

案例频道

案例频道